This paper dives into 7 tips and tricks to what makes DDRx challenges so complicated, their cost, and what you can do to resolve them. You do not have to be an expert to analyze DDRx interfaces like a pro!

7 tips to DDRx interfaces

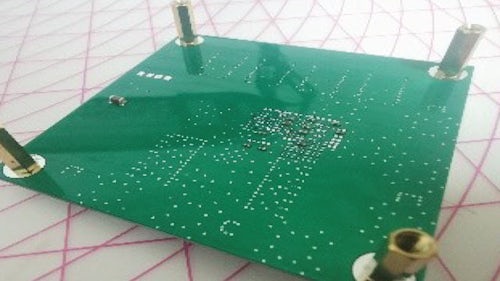

- Today’s technology could not exist without DDRx interfaces

- As performance increases, design complexity also increases

- Every design is different, so engineers need confidence their DDRx design will work as intended

- Design analysis is a fundamental part pf product success

- Costly design respins could slow you down

- Complete DDRx validation includes analysis of all signal-quality requirements and signal/group timing relationships

- Using the HyperLynx DDR wizard interactively walks you through how to set up parameters to run simulations

Learn more on HyperLynx DDRx Simulation