白皮書

Calibre nmLVS-Recon 技術加速產品上市時間

提高早期 SoC 整合中 LVS 電路驗證的生產力並減少上市時間

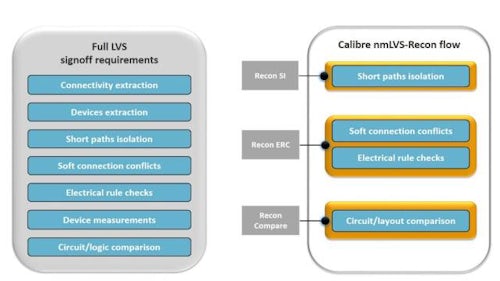

為了滿足緊迫的上市時程,SoC 設計師必須經常在個別區塊完成前,甚至在可用之前,就匆忙地開始他們的晶片整合。包含嚴重系統違規(如 net 短路)的設計,不僅會產生數以千計的錯誤結果,而且還會因為需要大量的硬體資源而延長整個 LVS 疊代的執行時間並降低可擴充性。Calibre nmLVS-Recon 解決方案將更直覺的方法引入早期階段的電路驗證,僅僅執行解決優先順序最高之問題所需的檢查。 工程師可在不同配置間輕鬆切換,並決定自己在每一輪執行中想要專注在哪些問題上。Calibre nmLVS-Recon 流程會自動決定必須執行哪些電路驗證要求,以實現最大效率。驗證工程師可以使用 Calibre nmLVS-Recon 流程以交互疊代的方式快速有效地發現並修復這些類型的違規,直到設計已預備好執行全晶片 Signoff LVS 疊代作業為止。Calibre nmLVS-Recon 技術不僅大幅加快了整個電路驗證檢查流程,而且可透過供應多組態架構增加使用模型的靈活性,進一步減少驗證 TAT 與上市時間。