白皮书

将 2.5D/3DIC 物理验证提升到更高水平

Calibre 3DSTACK 工具有助于提高 2.5D 和 3D IC 物理验证的速度、准确性和易用性

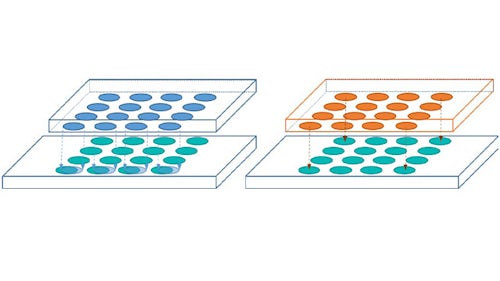

伴随多裸片、多小芯片堆叠配置的使用,西门子 EDA 对 2.5/3D IC 验证的支持也在同步发展。我们增强了 Calibre 3DSTACK 检查,以确保更准确地检查裸片之间的对齐情况,并增加了预检模式,支持工程师在调用 signoff 运行之前捕捉多种设置/数据问题。在调用 Calibre 3DSTACK signoff 运行之前查找并更正基本实现差错和系统性错误,可以消除不必要的调试迭代,并加快整体封装的验证流程。

此外,Calibre 3DSTACK 与 Xpedition Package Designer 和 Substrate Integrator 工具的集成,有助于加快实现速度,与此同时,与业界领先的寄生参数提取工具的结合,还可以捕获裸片或封装接口之间的耦合。通过扩展其他传统 IC 验证工具,如可靠性验证,来识别和解决封装问题,设计公司能够进一步提高其高密度先进封装产品的市场价值。