백서

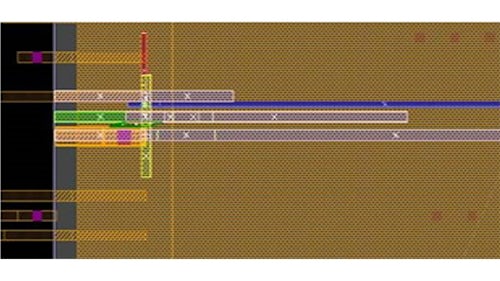

Calibre RealTime Digital 설계 내 DRC를 통해 P&R에서 더 빠른 사인오프 DRC 통합을 달성하는 Qualcomm

Calibre RealTime Digital 사인오프 물리적 검증으로 P&R 환경 내에서 더 빠른 사인오프 통합을 달성하세요.

이제 구현 환경에서 Calibre 사인오프 DRC를 반복할 수 있어 Qualcomm 설계자들은 주요 설계 일정 중에 최소 3~5회의 DRC 클로저 반복을 줄일 수 있으며, 이를 통해 대규모 SOC 설계의 테이프아웃 사이클을 몇 주 단축할 수 있습니다. 또한 Calibre RealTime Digital 인터페이스는 기존의 물리적 검증 흐름에서 사용되는 것과 동일한 Calibre nmDRC™ 사인오프 데크와 엔진을 사용하기 때문에 Qualcomm은 설계가 모든 제조 요구 사항을 충족할 것을 확신할 수 있습니다. 어떤 사용 모델을 적용하든 간에 Calibre RealTime Digital 인터페이스를 통해 Qualcomm 엔지니어는 DRC 오류를 수정하는 데 걸리는 시간을 줄임으로써 혁신적인 고품질 설계를 생성하는 데 더 많은 시간을 투자하고, 그러한 설계를 예정에 맞게 출시할 수 있습니다.