백서

지오메트리 검사를 넘어 - 회로 인식형 설계 검증

Fast, accurate, automated context-aware checking in all phases of IC design verification

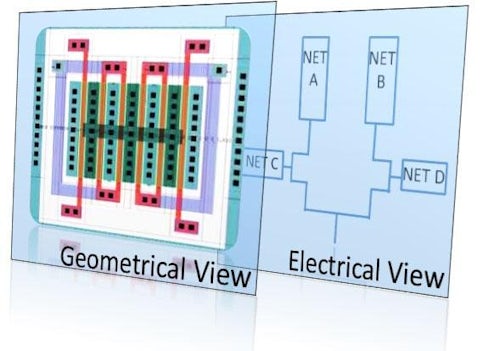

Automated context-aware checking has become an essential best practice for providing reliable and timely IC chips to the market. Designers can leverage the actionable net/device debug information in error results to more quickly and easily adjust layouts based on both the electrical and geometrical features in an IC design, improving both verification precision and debugging efficiency. Physical, circuit, electrical, and reliability IC design verification can all take advantage of context-aware checks to improve the quality and accuracy of results, while reducing turnaround time.