백서

Circuit Verification의 새로운 패러다임인 Calibre nmLVS-Recon 테크놀로지를 통해 출시 시간을 앞당겨보세요.

초기 단계 SoC 통합에서 LVS 회로 검증 생산성을 향상하고 출시 시간을 앞당겨보세요.

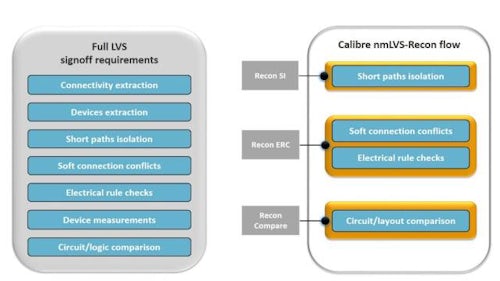

촉박한 시장 일정을 맞추려면 SoC 설계자는 개별 블록이 완성되거나 심지어 사용할 수 있게 되기 전이더라도 칩 통합 작업을 서둘러서 시작해야 합니다. 중대한 시스템 위반(예: Short된 넷)을 포함하는 설계는 수천 개의 오류 결과를 생성할 뿐만 아니라 광범위한 하드웨어 리소스를 필요로 하기 때문에 전체 LVS 반복의 런타임 및 확장성을 저하시킵니다. Calibre nmLVS-Recon 솔루션은 가장 우선순위가 높은 문제를 해결하기 위해 필요한 검사만 실행할 수 있도록 초기 단계의 circuit verification에 더욱 직관적인 접근 방식을 도입합니다.

엔지니어는 서로 다른 구성을 쉽게 전환할 수 있으며, 모든 실행 단계에서 어떤 문제에 초점을 맞출지 결정할 수 있습니다. Calibre nmLVS-Recon 프로세스는 최대 효율성을 위해 실행해야 하는 circuit verification 요구 사항을 자동 결정합니다. 설계 팀은 full-chip signoff LVS 작업을 위한 설계가 준비될 때까지 Calibre nmLVS-Recon 프로세스를 사용하여 이러한 유형의 위반을 반복적이고 인터렉티브한 방식으로 빠르게 효율적으로 찾고 수정할 수 있습니다. Calibre nmLVS-Recon 테크놀로지는 전체 circuit verification 검사 프로세스를 근본적으로 가속화할 뿐만 아니라 사용 모델 유연성을 제공하는 다중 구성 프레임워크를 제공함으로써 검증 TAT 및 출시 시간을 더욱 단축합니다.