2.5D/3D IC latch-up prevention: an automated verification strategy

Automated verification of 2.5/3D IC latch-up prevention

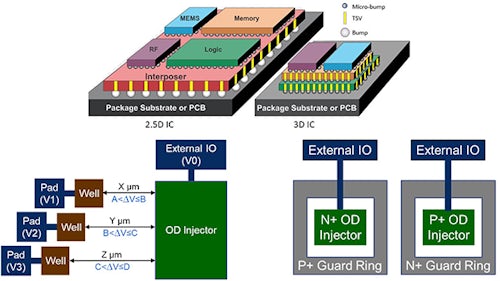

With the Calibre PERC reliability platform, an automated 2.5/3D IC latch-up prevention verification methodology is available that addresses the multiple challenges inherent in advanced latch-up protection for multi-die packages. A topology-aware flow applies external latch-up design rules, while a voltage-aware flow applies mixed-voltage latch-up design rules across all levels of a 2.5/3D IC layout. These flows are based on automated identification of external IOs at the assembly level, without the use of any manual layout markers on the die level. Implementing an automated latch-up protection verification solution for 2.5/3D IC designs ensures accurate and consistent latch-up protection, improving the reliability and product life of these products.