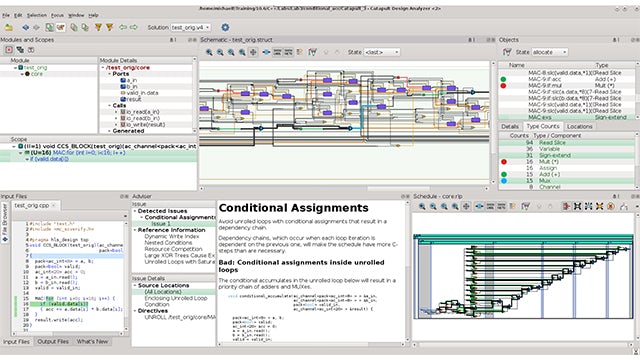

Catapult High-Level Synthesis resource library

Be it deep learning, computer vision, communications, video, or countless other spaces, Catapult is more than just “C to RTL”. ASIC, FPGA or eFPGA, with novel code/functional coverage, class-leading power opt, and formal verification, learn how it enables you to do more, and do it better.