Improving design reliability: LEF/DEF IO ring check automation

A holistic, integrated, automated approach to SoC IO ring placement verification

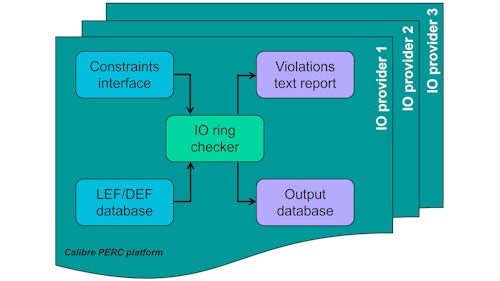

In collaboration with ARM, Siemens EDA developed an automated framework to verify SoC compliance with IO placement rules, using the Calibre® PERC™ reliability platform. The Calibre PERC platform can combine both the geometrical and electrical constraints of a design to perform complex rule checks that incorporate layout restrictions based on electrical constraints or variations. This flexible and automated approach to IO pad ring placement verification allows designers to focus on their design, using the IO ring checking framework and the Calibre PERC reliability platform to confirm the validity of the layout they create. The ability to perform this validation on LEF/DEF designs allows early completion of this task in the design cycle, while there is still an opportunity to optimize and refine the design before beginning final signoff verification.