Four ways to optimize IC layout load time without capital investment

Proven strategies reduce IC design layout load times for physical verification and debugging with existing hardware resources

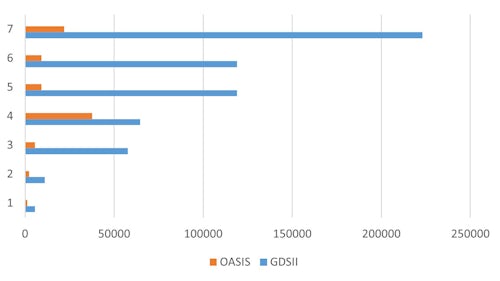

With more design content being added to chips at advanced technology process nodes, increases in layout file size and load times are impacting tapeout schedules for many companies. However, resource management is a critical element of productivity. Before purchasing expensive hardware and storage, companies should consider adopting proven strategies to optimize layout loading time for physical verification and debugging. Techniques such as switching to the OASIS file format and excluding unnecessary properties when loading layout files can be implemented using existing resources. The Calibre DESIGNrev chip finishing platform provides multiple options that enable design teams to further reduce file size, load time, and memory usage, allowing them to optimize the use of their existing resources. Companies who take advantage of proven functionality can achieve significant productivity gains without incurring the time and expense of significant capital investments.