white paper

Debugging P2P interconnect resistance errors using resistance segmentation

Debugging P2P results through interconnect resistance segmentation with Calibre® PERC™ reliability verification

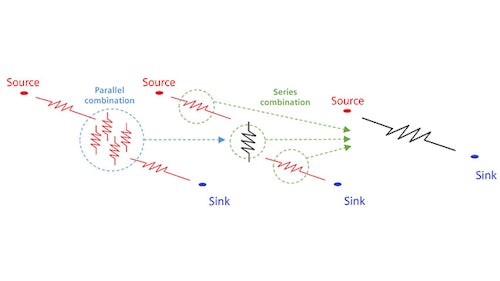

A P2P simulation finds and reports nets that exceed a predefined resistance threshold for various device interconnect paths. When a P2P interconnect resistance error is significantly higher than expected, which indicates there may be a routing mistake or a false violation, designers must be able to identify which segment of a reported pin-pair path is contributing to the high resistance value. Using the Calibre PERC coordinate-based P2P simulation segmentation flow to segment a net lets designers quickly isolate and identify the high resistance point causing a P2P resistance violation in an IC layout, providing a fast, effective means of reducing time spent debugging and fixing P2P resistance violations in an IC layout.