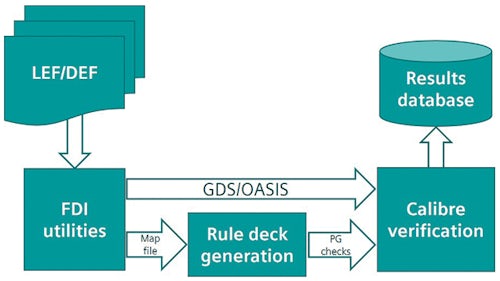

SoC parallel design implementation flows often contain data of varied completion and quality. Managing data consistency through data format conversions is difficult and time-consuming. To ensure fast, efficient analysis of critical early-stage design issues, the Calibre nmPlatform includes LEF/DEF read/write capabilities and a robust mapping infrastructure that enables the high-performance Calibre PV and DFM tools to run with LEF/DEF data. Using LEF/DEF data in early-stage verification reduces overall TAT while enabling the development of targeted solutions.

Data format flexibility in early-stage SOC design verification and optimization optimizes use of faster targeted solutions while ensuring design quality

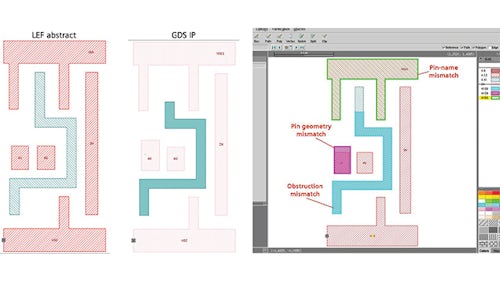

Managing parallel SoC design implementation and integration flows means managing design data at different stages of completion and quality. While P&R tools typically use LEF/DEF data, signoff physical verification and DFM tools have traditionally required GDS/OASIS data formats. Multiple data conversions in parallel flows means LEF/DEF data often falls out of sync with its OASIS/GDS counterpart, leading to large numbers of DRC violations and inaccurate DFM modifications. Because Calibre nmPlatform signoff tools can read and write LEF/DEF data in customized early-stage DRC checks and DFM operations, design teams can more quickly and accurately pinpoint systemic design flaws without running foundry rule decks, and back-annotate design optimizations into P&R with confidence, while maintaining parallel SoC design flows for speed and efficiency.