white paper

Customize and standardize your IC verification configuration

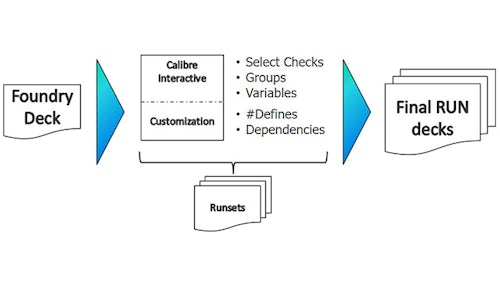

Optimizing signoff physical verification run configurations with Calibre interfaces

Considering the number of Calibre verification runs designers launch in a tapeout cycle, even modest gains in efficiency can represent significant gains in productivity. By enabling the creation of run configurations in a consistent, easy-to-use visual environment, Calibre interface tools eliminate multiple time-intensive manual tasks, freeing up more time for designers to focus on meeting design goals and tapeout schedules. The Calibre toolsuite provides several interface tools, including the Calibre Interactive invocation GUI, the Calibre RVE results viewer, and the Calibre DESIGNrev chip finishing interface, that enable designers to manage these tasks easily and accurately.