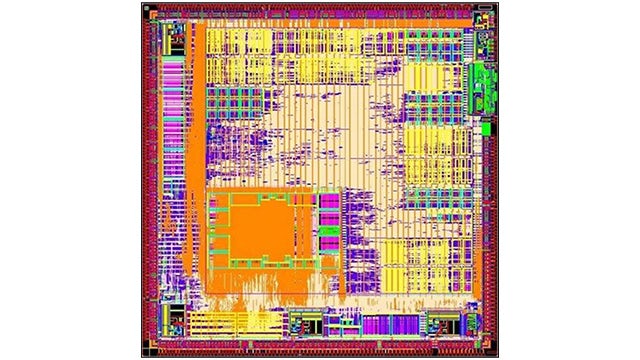

At each new process node, early chip-level verification of SoC layouts is often time-consuming and frustrating. Targeted IC verification of early layouts can enable teams to focus on fixing critical and high-impact errors, reducing runtimes and total cycle time. The Calibre nmDRC Recon technology provide a focused, intelligent selection of DRC rules and layout subsets that help pinpoint crucial systemic design issues. Running targeted DRC verification in early SoC design layouts enables design teams to quickly and effectively find and fix these critical errors early in the design cycle.

Early-stage SoC verification productivity enhanced by selective DRC verification strategies

Each new process introduces a whole new range of verification requirements and challenges —new design rules that enable desired design pitches; physical phenomena that is new or was previously immaterial, new and changing impacts on electrical behavior, new interconnects and device materials, ad infinitum. This plethora of data can overwhelm design teams during early-stage SoC verification. In response, the EDA industry has taken steps to provide designers with only the information they need at the time they need it.

Running full-chip signoff DRC verification on early SoC layouts typically creates thousands to millions of errors, many of which will turn out to be irrelevant to the early design process, wasting time and resources as designers attempt to debug them. Intelligent automated pre- and post-processing minimizes the set of rules to be run, and applies them to subsets of the layout data. By reducing both the runtime and overall number of iterations, as well as making it easier for designers to understand and fix the root cause of crucial DRC errors, the “construct by correction” approach of tools such as the Calibre nmDRC Recon technology are moving the semiconductor industry closer to a fully-realized design automation infrastructure.