white paper

Automated waiver management for IC reliability verification

Automated error waiver management enhances IC design reliability verification

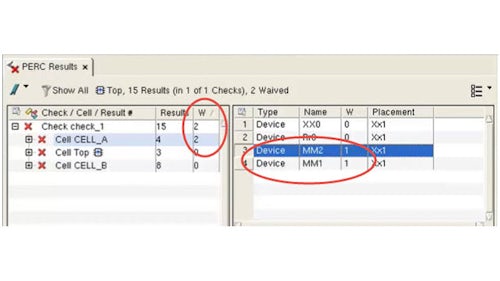

Calibre PERC automated waiver processing supports both IP and full-chip waivers management in IC design reliability verification The unique technology enables accurate processing of waivers that combine topological and geometrical information. Not only can waivers be automatically generated, but a controlled process flow supports multi-user waiving while ensuring design integrity.